今回利用した HP Z3816A は主にアメリカ合州国の CDMA 携帯電話の基地局の同期用に 使われた周波数標準器で、hp (現 Agilent) がこの部門を Symmetricom に売却 するのに伴ってか、一時期中古市場に沢山放出されたもののひとつである。 この標準器は内蔵のオーブン補償水晶発振器 (OCXO) の長期にわたる周波数を調整する ための正確なタイミングデータを GPS 衛星を追跡することにより得ている。 GPS に同期しているときには 1e-12 / day 程度、保持モードのときでも 内蔵 OCXO (MTI 260 シリーズ) の性能より 1e-10 / day 程度の周波数精度が期待出来る。 この装置から出力される 1 秒パルス (PPS) 信号は GPS に同期しているときには 協定世界時 (UTC) から 1μs 以内になっている(TFOM = 3 の時)。 またシリアルポートからは 時刻予告出力等が得られるので、このデータと PPS 信号をワークステーションに 入力してやることにより安価かつ簡単に Stratum 1 NTP サーバーを構築することが出来る。 ワークステーションには、コストパフォーマンスとそのマザーボードの作りの良さから hp のデスクトップ PC MT d330 uT を オペレーティングシステムには、PPS-API で一日の長がある FreeBSD を採用した。

[重要 : アンテナは後に交換した。 §13 参照のこと]

まずはアンテナを設置しなければ話は始まらない。近所で サン電子の(衛星放送受信パラボラアンテナ用)マスト SAB-500J を調達して、 hp の GPS Antenna Assembly HP 58504A をマウントした。

[fig.1 HP 58504A annterna and mount base]

マストの上端から 11mm のところに M5 のタップを 120°間隔で 2 箇所切って アンテナ本体には 3M の VEM313 を W20 x L100 を巻いてスペーサ兼ダンパーにし、 アンテナとマストトップ間には t1 x D42 のオレフィン系エラストマー(Olefin Plastic Elastomer)ゴムを入れた。

[fig.2 HP 58504A anntena]

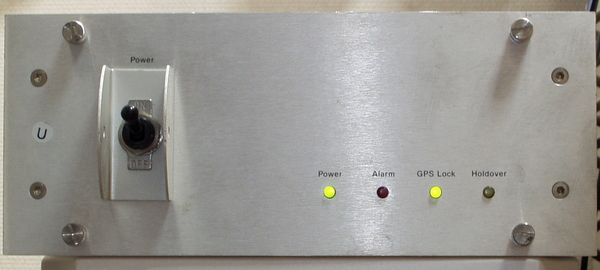

HP Z3816A にアンテナを接続し、電源を入れて1時間程で GPS に同期したところ。 今までに学習していた内部のキャリブレーションデータが壊れるおそれがあるので、 アンテナを接続せずには電源を入れない方が良い。この場合や、 適切なアンテナが正しく接続されていないときなど、アンテナへの供給電流が規定の 範囲外の場合には Alarm が点灯するはずである。

[fig.3 Z3816A front pannel]

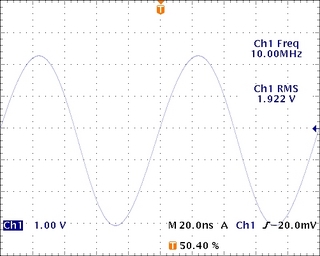

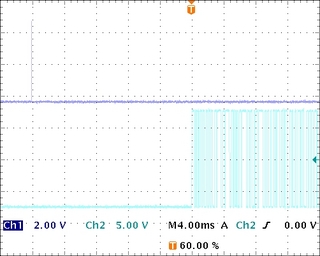

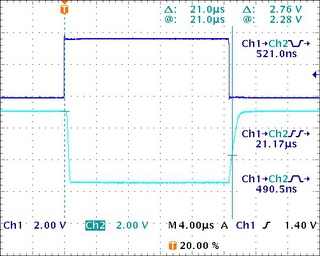

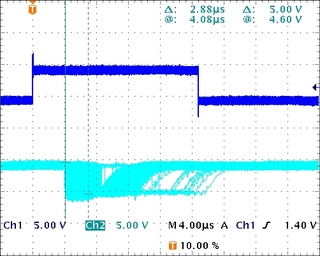

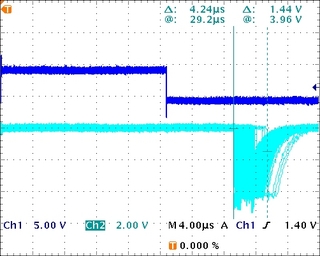

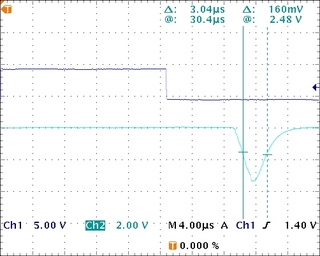

出力を確認してみた。10MHz 出力は 50Ω 出力であるが、 PPS 出力は 0-5V のロジックレベル出力のようである。 図示していないが 19.6608MHz 出力 も 0-5V のロジックレベルであった。

| [fig.4 Z3816A 10MHz Output (Rload=10MΩ||13.3pF)] | [fig.5 Z3816A PPS→Serial output delay] |

|

|

[重要 : PPS はアップエッジでキャプチャされる。 §11, §14 参照のこと]

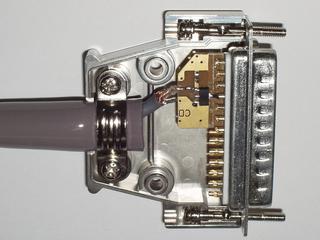

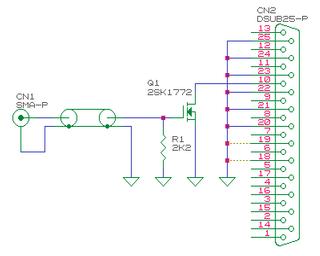

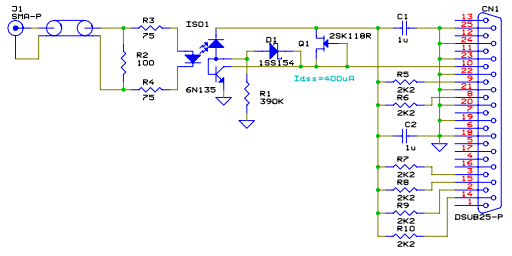

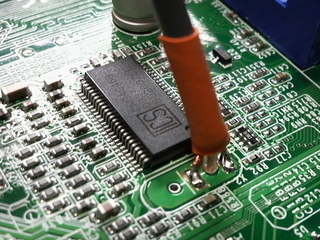

ntpd で kernel PPS を使用出来るようにするため PPS-API 用に、 サーバーのパラレルポートの *Ack 入力に (Z3816A の) PPS をインバートして接続する インターフェース (以下 PPS-I/F) を次の様に作成した。 手元の部品で間に合わせに作ったのだが、 パラレルポートの入力がプルアップされていることを利用して オープンドレイン接続にしたため、別に電源を必要としないのは利点である。 FET には RENESAS の高速度電力スイッチング用 (4V 駆動) MOS FET 2SK1772 を使用した。

[fig.6 Z3816A PPS-I/F]

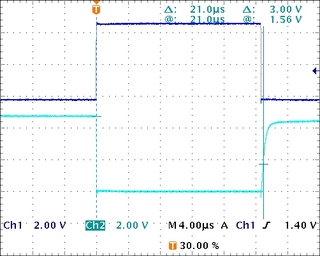

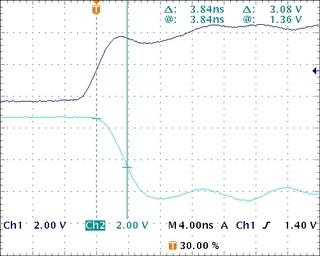

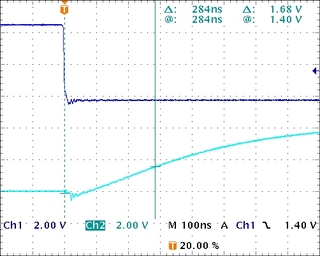

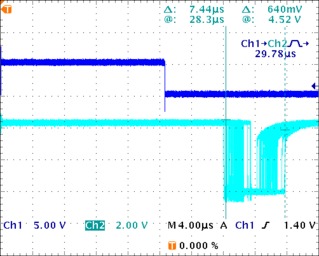

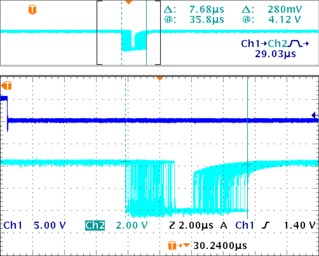

インターフェースケーブル長は 0.67 m である。 整合されているわけでは無いのであまり長くすることは出来ない。 PPS-I/F の回路図と、サーバーのパラレルポートに接続した状態での測定結果を次に示す。 [Jun. 8, 2005]

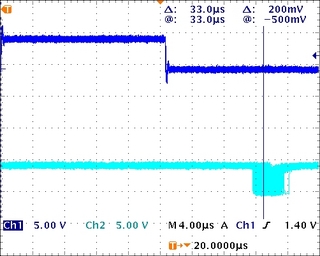

| [fig.7 PPS-I/F schematic] | [fig.8 PPS PPS-I/F input/output waveform (Input=Z3816A PPS)] |

|

|

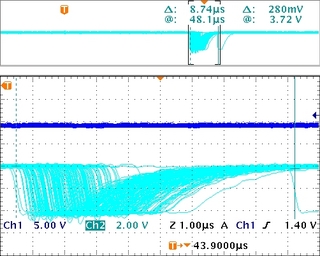

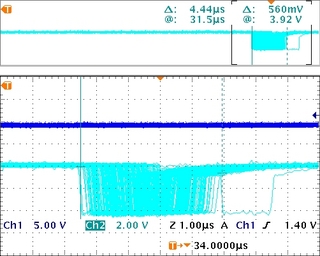

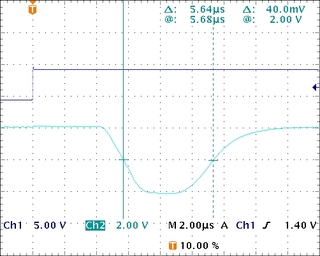

| [fig.9 PPS-I/F turn-on delay (BW > 100MHz)] | [fig.10 PPS-I/F turn-off delay (BW > 100MHz)] |

|

|

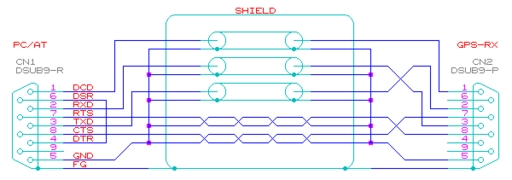

後日、隣の部屋にある Stratum2 の NTP サーバーのために PPS信号をフォトカプラで絶縁して接続するインターフェースを作成した。 別に電源を用意しないで済むように、アナログ伝送用のフォトカプラ Avago (旧 Agilent (旧 Hewlett Packard)) の 6N135 を用い、 フォトダイオードのバイアスは、パラレルポートの入力プルアップから得ている。 立上り時間の改善のために出力トランジスタを東芝のミキサ用ショットキーバリアダイオード 1SS154 でクランプし、 また、ベースに蓄積電荷の放電用の抵抗を追加してある。 基板は他の用途に作成していたものを流用した。

| [fig.11 Isolated PPS I/F ] | [fig.12 Isolated PPS I/F propagation delay] |

|

|

| [fig.13 Isolated PPS I/F schematic] |  |

Z3816A と PC 間のシリアル接続用ケーブルは手元にあった次のような接続の クロスケーブルを使用したが、 Z3816A にはフロー制御信号の RTS/CTS は無いので、 この接続 (7, 8 ピン) は不要である。 PC 側の DSR-DTR (6, 4 ピン)の接続は、アプリケーションによってはこの接続が無いと シリアルポートが使えない場合があるのであった方が良い。 Z3816A の DCD ピンは N.C. になっているので PPS 信号を後述の DCD ピンから PC に入力したい場合には別途接続する必要がある。

[fig.14 GPS serial connection cable]

PPS-API 用にはシリアルポートの DCD (Data Carrier Detect) 入力に入れた PPS 信号も扱うことができるが、 シリアルポートには通常、数100kHz 以下の帯域制限がかかっているため μs オーダーで遅延が増加する可能性がある。それで今回はパラレルポート接続にしたが、 シリアルポート接続にする場合、MAX232A などの昨今の RS-232C インターフェース IC のレシーバでは、スレッショルド電圧がほぼ TTL 互換になっているものが多く DCD 入力に Z3816A の PPS 出力の様な 0-5V の PPS 信号を (接続ケーブル長が短かいのならば) 直結できるものも多い。 この場合 RS-232C ドライバを余分に使わずに済むのでその分 (数 100ns オーダー) の遅延が発生せずに済む。

実際に Z3816A の PPS をいくつかの PC のシリアルポート (の DCD) に接続して、

Part number VTL(min) [V] VTH(max) [V] Hysteresis(typ) [V] ADM222/232A/242(5V) 0.8 2.4 0.4 MAX232A(5V) 0.8 2.4 0.5 MAX3380E(3.3V) 0.6 2.4 0.3 MAX3380E(5V) 0.8 2.4 0.3 MAX3222E/3232E(3.3V) 0.6 2.4 0.5 MAX3222E/3232E(5V) 0.8 2.4 0.5

./ntp-4.2.0/util/pps-api /dev/cuua0のようにして確かめてみたが、どれも PPS 信号を取得出来ているようであった。 [Jun. 10, 2005]

[重要 : PPS はアップエッジでキャプチャされる。 §11, §14 参照のこと]

FreeBSD に実装されている PPS-API ではモニター用に PPS 割り込みに対する

応答信号(エコー)を発生させることができるので、

測定用に ./ntp-4.2.0/util/pps-api /dev/pps0 を実行させて観察した。

PPS-I/F に接続した Z3816A の PPS 信号からエコーまでの遅延時間の様子を

fig.15, fig.16 に示す。

エコーはパラレルポートのオートラインフィードピン (fig.7 では CN2 の 14 ピン) に出力される。

[table.1 披測定装置(D.U.T.1)諸元]

ワークステーション Hewlette Packard MT d330 uT プロセッサ Intel Pentium4 processor 2.4C (200MHz FSB, 512KB L2 cache) チップセット Intel i865G 主記憶装置 Samsung K4H560838E-TCCC 512MB * 2 (DDR400-3-3-3-8) 外部記憶装置 HGST HDS722516VLAT80 * 2(160GB RAID1/Promise FastTrack TX2000) オペレーティングシステム FreeBSD-4.11-STABLE 特記事項 kernel compiler and its options

gcc version 2.95.4 20020320 [FreeBSD]

COPTFLAGS = -O -march=pentium

Hyper Threading Technology is enabled by BIOS and sysctl

machdep.hlt_logical_cpus=0

machdep.hyperthreading_allowed=1

| [fig.15 PPS→Echo delay (D.U.T.1, fcore=2.4GHz)] | [fig.16 PPS→Echo jitter (D.U.T.1, fcore=2.4GHz)] |

|

|

[table.2 披測定装置(D.U.T.2)諸元]

ワークステーション Tyan S5101ANNRF プロセッサ Intel Pentium4 processor 3.0 (233MHz FSB, 512KB L2 cache) チップセット Intel i875 主記憶装置 Samsung K4H560838E-TCCC 512MB * 2 (DDR466-3-4-4-8) 外部記憶装置 HGST HDS722516VLAT160 * 4(320GB RAID0+1/Promise FastTrack TX2000) オペレーティングシステム FreeBSD-4.11-STABLE 特記事項 kernel compiler and its options

gcc version 2.95.4 20020320 [FreeBSD]

COPTFLAGS = -O -march=pentium

Hyper Threading Technology is enabled by BIOS and sysctl

machdep.hlt_logical_cpus=0

machdep.hyperthreading_allowed=1

| [fig.17 PPS→Echo delay (D.U.T.2, fcore=3.5GHz)] | [fig.18 PPS→Echo jitter (D.U.T.2, fcore=3.5GHz)] |

|

|

Z3816A の設定はシリアルポートから行う。

余談だが連続モードのときには1秒ごとに出力されるデータのフォーマットは F1 になるようである。

コマンド コメント :SYSTem:COMM:SER1:BAUD 9600;PARITY NONE シリアル通信速度を標準設定の 9600 Baud パリティ無しに設定 *CLS エラー解除 PTIMe:TCODe:CONT 0 非連続モードに設定 :SYSTem:COMM:SER1:FDUP 0 デュプレックスをオフに設定 :DIAG:GPS:UTC 1 UTC 時間に設定 :PTIMe:TCODe:FORMat F2 出力フォーマットを F2 に設定

コマンド コメント 結果 *IDN? 製品 ID HEWLETT-PACKARD,Z3816A,3710A00335,4001-A :DIAG:IDEN:GPS? 内部 GPS 受信器 ID "COPYRIGHT 1991-1997 MOTOROLA INC.", "SFTW P/N # 98-P36848P ", "SOFTWARE VER # 3 ", "SOFTWARE REV # 1 ", "SOFTWARE DATE May 28 1999", "MODEL # R5122U1154 ", "HWDR P/N # 5 ", "SERIAL # R06OIE ", "MANUFACTUR DATE 9L08 ", ":SYSTem:STATus? フォーマット済み ステータス出力 …省略… (HP SATSTAT と同様)

[重要 : PPS インターフェースを変更してみるのに伴い /usr/src/sys/dev/ppbus/pps.c も変更した。§14 参照のこと]

FreeBSD-4.11-STABLE

カーネルのコンフィギュレーションファイルに次の行を追加/修正してカーネルをコンパイル、インストール。

PPS 信号をパラレルポートの *ack (Dsub25-10) に接続している場合には pps デバイスが必要。

シリアルポートから取得する時刻のジッタは

シリアルポートの FIFO を使用しないようにした方が低減出来たが

所詮 ms オーダーのことで、

時刻精度の方は PPS に任せるのでこれはあまり気にしなくて良い。

options PPS_SYNC device pps # Pulse per second Timing Interface device sio0 at isa? port IO_COM1 flags 0x02 irq 4 # disable FIFO

cd /usr/src make buildkernel make installkernel reboot

デバイスファイルの作成

GPSレシーバのシリアル入出力を PC の COM1 に接続していて、PPS 信号はパラレルポート0 の *Ack に接続している場合。

cd /dev/ ln -s /dev/cuaa0 /dev/hpgps0 sh MAKEDEV pps0

ntp-4.2.0 を ATOM と HPGPS ドライバ付きで configure してコンパイル、インストールする。

cd ntp-4.2.0/ ./configure --enable-ATOM --enable-HPGPS make make install

ntpd がリファレンスクロックを参照するように /etc/ntp.conf を設定し、 システムに合わせて遅延補正値も設定する。 kernel PPS を利用するには PPS ドライバの flag3 をセットする。 ついでにログファイル関係も設定する。

[/etc/ntp.conf の設定例 (ristrict 関係は省略)]

logfile /var/log/ntp.log driftfile /etc/ntp.drift statsdir /var/log/ntpstats/ statistics loopstats peerstats clockstats filegen loopstats file loopstats type day enable filegen peerstats file peerstats type day enable filegen clockstats file clockstats type day enable # Atomic pulse per second interface # Fudge flag3 controls the kernel PPS discipline: 0 for disable (default), 1 for enable. # Fudge time1 is used to compensate the PPS acquisision delay. server 127.127.22.0 prefer fudge 127.127.22.0 flag3 1 time1 0.000028 # GPS_HP # Fudge time1 is used to accomodate the timecode serial interface adjustment. # 20.1ms + 25ms (24 characters at 9600 bps) # Fudge flag4 can be set to request a receiver status screen summary, which # is recorded in the clockstats file. server 127.127.26.0 prefer fudge 127.127.26.0 time1 -0.9549 flag4 1 # Public stratum2 servers server ntp1.jst.mfeed.ad.jp server ntp2.jst.mfeed.ad.jp server ring.nict.go.jp # Local clock server 127.127.1.0 fudge 127.127.1.0 stratum 10

ntpd で PPS が正しく使えているか確かめるには、ntpd を起動した後 しばらく後に ntptime で確認した status に PPSSIGNAL が立ち、それから PPSTIME と PPSFREQ が立っていくのを確かめれば良い。

[ntptime 実行結果の例]

ntp_gettime() returns code 0 (OK) time c679dc18.3421e1c0 Sat, Jul 9 2005 14:16:08.203, (.203642110), maximum error 8390 us, estimated error 2 us, TAI offset 0 ntp_adjtime() returns code 0 (OK) modes 0x0 (), offset 0.754 us, frequency -0.003 ppm, interval 256 s, maximum error 8390 us, estimated error 2 us, status 0x2107 (PLL,PPSFREQ,PPSTIME,PPSSIGNAL,NANO), time constant 6, precision 0.001 us, tolerance 496 ppm, pps frequency -0.003 ppm, stability 0.006 ppm, jitter 1.012 us, intervals 2178, jitter exceeded 339, stability exceeded 0, errors 0.

status 0x2101 (PLL,PPSSIGNAL,NANO), ↓ status 0x2141 (PLL,UNSYNC,PPSSIGNAL,NANO), ↓ status 0x2341 (PLL,UNSYNC,PPSSIGNAL,PPSJITTER,NANO), ↓ status 0x2307 (PLL,PPSFREQ,PPSTIME,PPSSIGNAL,PPSJITTER,NANO), ↓ status 0x2107 (PLL,PPSFREQ,PPSTIME,PPSSIGNAL,NANO),

ログファイルも結構大きくなるし ntpd には無用なのでセットしない方が良いと思うが、

hpgps ドライバで flag4 をセットしておくと HP SATSTAT と同様のフォーマット済みステータス出力が

次の様に clockstats ファイルにロギングされる。

[フォーマット済みステータス出力]Z3816A の稼働を開始して2ヵ月程で Holdover Uncertainty Predict が 2μs 程から 1μs 程に減って来ているのだが、 これは hp SmartClock (TM) Technology の学習効果だろうか。[Sep. 2, 2005]

------------------------------- Receiver Status ------------------------------- SYNCHRONIZATION ............................................. [ Outputs Valid ] SmartClock Mode ___________________________ Reference Outputs _______________ >> Locked to GPS TFOM 3 FFOM 0 Recovery 1PPS TI +100 ps relative to GPS Holdover HOLD THR 1.000 us Power-up Holdover Uncertainty ____________ Predict 900 ns/initial 24 hrs ACQUISITION ................................................ [ GPS 1PPS Valid ] Tracking: 5 ____ Not Tracking: 3 ________ Time ____________________________ PRN El Az C/N PRN El Az LOCAL 13:59:42 02 Sep 2005 1 56 311 44 *14 78 191 GPS 1PPS Synchronized to UTC 5 17 51 38 *16 13 235 ANT DLY 50 ns 6 49 120 45 *22 11 198 Position ________________________ 25 43 309 40 MODE Hold 30 51 41 53 LAT N 35:xx:xx.xxx LON E 139:xx:xx.xxx HGT +50.83 m (GPS) ELEV MASK 10 deg *attempting to track HEALTH MONITOR ......................................................... [ OK ] Self Test: OK Int Pwr: OK Oven Pwr: OK OCXO: OK EFC: OK GPS Rcv: OK

[ 重要 ] 最初は PPS-API の PPS_CAPTUREASSERT っていうのは パラレルポートの *Ack 入力のロジックレベルが 'Low' に なったときにアサートされると思っていたのだが 測定してみると逆で実はアップエッジでの割り込みになっていた。 ntp.conf には PPS の前縁(アップエッジ)からの遅延補正値を指定しているので ntpd の動作上には変わりが無いが微妙に気にくわない。 /usr/src/sys/dev/ppbus/pps.c を見ると割り込み時に *Ack 入力のレベル確認を しているようだが、これだとパルス幅の短い PPS 信号は取得できないので問題である。 実際、fig.7 のように入れてある(オープンドレイン)インバーターを入れなかった 場合には fig.8 の PPS 信号はうまくキャプチャ出来なかった。 普通は負論理の信号をアサートすると言えば 'Low' にすることだと言うのは 置いておいても、なぜこんな非常識っぽい (プルアップされている負論理 TTL 割り込み入力を正論理で使うと ノイズマージンが減少するし、アップエッジのジッタはダウンエッジに比べて多いし、 後段のレジスタでメタステーブルが発生する確率も高い) 方を選んでいるのかわからない。割り込みコントローラの都合なのか? この辺りの事情をご存知の方は教えて頂けると幸いである。 [Jul. 13, 2005]

ntpd から見て GPS_HP(0) の jitter が 4 ms 程度と余り良くないので Z3816A との通信速度を 19.2k baud に変更して ntpd にパッチをあてて試してみたが 余り違いは無かった。今は結局そのまま 19.2k buad で使用している。

まぁ、これは高精度の PPS(0) の方に同期していれば問題ないのだが、 NMEA ドライバ等と違い HPGPS ドライバはドライバの中から PPS-API を使って くれないので、ntp.conf の中で HPGPS と PPS の両方の server に対して prefer キーワードを付けなければ PPS(0) にロックし続けてくれなかった。

原因は不明だが ntp.conf の中で参照クロックだけを server にして、

それ以外の NTP サーバーを参照していないと

PPS を取りこぼしたかのような不安定な動作をすることがあった。

これは Z3816A との通信速度や SIO の FIFO の設定を変えても変化が無かった。

Local clock (127.127.1.0) を server 設定しておくというのでも大丈夫のようだが、

システムクロックにはホールドオーバーできるほどの安定度がないので

これを設定するのはためらわれる。

しかし、LAN の外側でのリンク断が発生した時にも上記の事象が発生するという事態が

生じたので、LAN 内にまで影響が及ぶのを防ぐためには

Local clock も server に設定しておいた方が良さそうだ。[Jul.17,2005]

[ntpq -p -c rv 実行結果の例 (PPS fudge time1 = 40μs)]

remote refid st t when poll reach delay offset jitter ============================================================================== oPPS(0) .PPS. 0 l 41 64 377 0.000 0.040 0.004 +GPS_HP(0) .GPS. 0 l 42 64 377 0.000 -0.292 3.379 LOCAL(0) LOCAL(0) 12 l 11 64 377 0.000 0.000 0.004 +xxx.xx.x-xxxxx. .GPS. 1 u 28 64 377 12.007 1.169 0.394 +xxxxx.xxxxx.xx. .GPS. 1 u 58 64 377 11.079 1.454 0.928 +xxxxx.x-xxxxxx. .PPS. 1 u 17 64 377 11.369 1.315 0.527 status=2174 leap_none, sync_atomic/PPS, 7 events, event_peer/strat_chg, version="ntpd 4.2.0@1.1161-lyuka56-z3816a-r Tue Jun 14 00:47:14 JST 2005 (18)", processor="i386", system="FreeBSD/4.11-STABLE", leap=00, stratum=1, precision=-18, rootdelay=0.000, rootdispersion=1.534, peer=20516, refid=PPS, reftime=c66d6915.f52e43d7 Thu, Jun 30 2005 3:38:13.957, poll=6, clock=c66d693e.a99b2281 Thu, Jun 30 2005 3:38:54.662, state=5, offset=0.040, frequency=0.007, jitter=0.001, stability=0.001

fig.15 や fig.16 のジッタの様子からみれば妥当であるが、 ntpd から見た PPS の jitter が 4μs 程度と当初予想していたより大きかった。 カーネルのコンパイルオプションとかで改善可能かも知れない。

ntpd の -N オプションを付けて優先度を上げておくと NTP クライアントから見て 若干ジッタが減るようである。

ワークステーションのシステムクロックはクロックジェネレータに接続された 水晶振動子で作られているため SPXO と同等の安定度しかないので、 これのジッタの影響も大きいのかもしれない(参考文献 5, 6 参照)。 PPS のキャプチャー時のジッタが μs オーダー、 システムクロックの変動による 1 秒ごとのジッタも μs オーダーと考えられるので、 今のところどちらが支配的とも言えない。fig.19 は ntpd の loopstats から見た オフセット変動の例である。

[fig.19 offset drift (SXO)]

その後、ワークステーションのシステムクロックジェネレータ ICS 952606 の 4, 5 ピン に接続されている水晶振動子を外して、その 4 ピンに TC74SHU04FU でバッファした 14.31818 MHz の VC-TCXO の出力を入力するように改造してみた。 といっても Z3816A の 10MHz にロックさせているわけではないので、 制御電圧は基準電圧 IC LM236-5.0 から生成した電圧を印加している。

[fig.20 offset drift (VC-TCXO)]

ntpd の loopstats でみると周波数安定度は数倍改善され、スパイク的なオフセットの

変動も若干減って今のところ ±8μs 以内に収まっているようである。[Jul. 1, 2005]

GPS アンテナを恒久設置とするために同軸ケーブル配管を敷設し、 アンテナを HP 58504A から HP 58532A に変更した。 58532A は 1575.42MHz ±50MHz で 60dB(typ) の減衰量の狭帯域 フィルタが入っていて雑音の多い都市部では有利と考えたからである。 58532 は狭帯域フィルタが入っている割に NF が 1.8dB(typ) と 58504A の 1.5dB(typ) に比べて遜色がほとんど無い。 ついでに同軸ケーブルも 50ns 遅延のケーブル (N 型コネクタ付き フジクラ 5D-FB 約12.14m) に 交換し、アンテナケーブル遅延も再設定 (:GPS:ADELay 5E-8) した。 5D-FB はそもそも屋外用ではないので屋内に引き込むところまでは外径 18mm の硬質ビニル電線管(未来工業 VE-14J2, N-14J) 等で 保護している。

| [fig.21 HP 58532A anntera] | [fig.22 wire protection bend] |

|

|

ところが、58532A を Z3816A に接続すると Z3816A の ALARM LED が点灯する。 エラーステータスを見て(:SYSTem:ERRor?)もエラー無しなので、K8CU のサイトでも報告のあったように アクティブアンテナへの電流が少なすぎるのが原因かと思い 5V での電流を 測ってみた。58504A が約 27.5mA に対して 58532A が約 17.5 mA と約 10mA 少なくなっていたのでやはり少なすぎるようだ。でもまぁ、 アンテナの故障検出以外に実害は無いので(今のところは)気にしないことにしている。

アンテナ交換のついでに VC-TCXO の制御電圧用基準電圧を TL431CLP とその定電流源 用の 2SK117BL に交換した。 TL431C のダイナミックインピーダンスが 0.2 Ω(typ) と LM236-5.0 に比べ 約 1/4 と低いので電源雑音に起因する変動が改善されるかもと考えたからである。 結果は、fig.23 のようにゆっくりとした変動もスパイク状の変動も随分改善されて ±4μs 以内になったように見える。同時にアンテナと制御電圧回路を変更したのでアンテナの特性と 基準電圧の特性のどちらがどういうふうに効いているのかはわからないが、 SPXO と 58504A より VC-TCXO と 58532A の方が良いのは間違いなさそうだ。 [Jul. 5, 2005]

その後一週間分のオフセット変動の統計をとったところ、サンプル数 N=9,390 で 標準偏差 σ=788ns であった。 5σ でも 3.94μs なのでオフセット変動は ±4μs 以内と言って良さそうだ。 [Jul. 10, 2005]

[fig.23 offset drift (VC-TCXO'+58532A)]

先に延べたようにシステムクロックの短期安定度は ntpd のポーリング間隔あたり PPS のジッタ未満であれば合理的とすれば 4μ / 64 から 3e-8 (per minute) 程度で十分といえる。 そう考えると SPXO では性能不足で TCXO で十分だろうということになって 今回の結果通りだが、PPS の取り込みジッタがもっと少ないとか ハードウェアタイムスタンパを使うのであれば システムクロック (14.318 MHz) は GPS レシーバの基準周波数出力にロックさせる (Z3816A の 10MHz * 63 / 44 = 14.318 MHz) 必要があるとも言える。[Jul. 6, 2005]

[list.1 /usr/src/sys/dev/ppbus/pps.c 変更箇所]

static void ppsintr(void *arg) { device_t ppsdev = (device_t)arg; device_t ppbus = device_get_parent(ppsdev); register struct pps_data *sc = DEVTOSOFTC(ppsdev); register struct timecounter *tc; register unsigned count; tc = timecounter; ppb_wctr(ppbus, AUTOFEED); count = timecounter->tc_get_timecount(tc); ppb_wctr(ppbus, IRQENABLE); pps_event(&sc->pps, tc, count, PPS_CAPTUREASSERT); }

| [fig.24 PPS→Echo jitter (D.U.T.1, fcore=2.4GHz)] | [fig.25 PPS→Echo average(256) (D.U.T.1, fcore=2.4GHz)] |

|

|

Agilent 53131A にて計測したところサンプル数 N=100, Vth=1.4V で、PPS→Echo の遅延は

であった。結局、PPS→時刻取得の遅延はおよそ 8μs 辺りかなというところか。 [Jul. 14, 2005]tdPPS↑Echo↓= 5.795μs (σ=794ns) tdPPS↑Echo↑=10.854μs (σ=765ns)

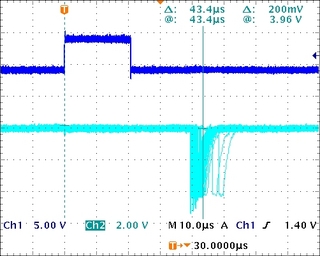

その後、このままで数日試してみたところ、原因は不明だが一日に数回の頻度で

数 10μs のスパイク的遅延が発生するようになり、またジッタもやや増加したので

元のインターフェースに戻し、pps.c も list.2 のようにエコー出力の前に時刻を取得するように変更した。

[Jul. 18, 2005]

[list.2 /usr/src/sys/dev/ppbus/pps.c 変更箇所]

static void ppsintr(void *arg) { device_t ppsdev = (device_t)arg; device_t ppbus = device_get_parent(ppsdev); register struct pps_data *sc = DEVTOSOFTC(ppsdev); register struct timecounter *tc; register unsigned count; tc = timecounter; count = timecounter->tc_get_timecount(tc); ppb_wctr(ppbus, AUTOFEED); ppb_wctr(ppbus, IRQENABLE); pps_event(&sc->pps, tc, count, PPS_CAPTUREASSERT); }

| [fig.26 PPS→Echo jitter (D.U.T.1, fcore=2.4GHz)] | [fig.27 PPS→Echo average(256) (D.U.T.1, fcore=2.4GHz)] |

|

|

先の計測結果と合わせて考えると間をとって結局 PPS→時刻取得の遅延は 28μs というところだが、 UTC に対してシステム全体で ±10μs くらいの時刻確度だろうか? [Jul. 19, 2005]tdPPS↑Echo↓= 30.598μs (σ=733ns) tpwEcho↓Echo↑=1.912μs (σ=50ns)

今回自宅に stratum1 を構築することになったのは、非対称な伝送速度の

通信路における ntpd の問題点を解決しようと色々と試していて

LAN 内に stratum1 が欲しくなっていたのと、それまで

外部の公開 NTP サーバーを利用して ±500μs 程度の安定度が

得られていたのが、ある日を境に地元 CATV 系の ISP とその上位間で 1 秒近い

ピーク遅延/ジッタが発生するようになってお話しにならなくなったのと、

また その ISP の兼ねてからの大雑把なメンテナンスに起因する年平均

1 ‰ を越えるリンクダウン率と回数に愛想をつかしたのがきっかけである。

今回自宅に stratum1 を構築することになったのは、非対称な伝送速度の

通信路における ntpd の問題点を解決しようと色々と試していて

LAN 内に stratum1 が欲しくなっていたのと、それまで

外部の公開 NTP サーバーを利用して ±500μs 程度の安定度が

得られていたのが、ある日を境に地元 CATV 系の ISP とその上位間で 1 秒近い

ピーク遅延/ジッタが発生するようになってお話しにならなくなったのと、

また その ISP の兼ねてからの大雑把なメンテナンスに起因する年平均

1 ‰ を越えるリンクダウン率と回数に愛想をつかしたのがきっかけである。

電源の保守の関係で NTP サーバーを下記のものに更新した。

それに伴い、VC-TCXO の制御基準電圧源を TL431C より安定度の高い (i.e. 0.5ppm/℃typ, 2ppm/Vtyp) Maxim MAX6325CSA に交換した。

また、VC-TCXO の温度による短期変動特性改善のため、温度勾配を減らし、かつ急な温度変動を緩和するために熱容量を増大させる目的で 65g の銅ブロックを VC-TCXO に付加した。

[table.3 披測定装置(D.U.T.3)諸元]

マザーボード Tyan S5102G3NR プロセッサ Intel Pentium4 processor 3.06 (133MHz FSB, 512KB L2 cache) チップセット Intel i875P 主記憶装置 Samsung K4H560838E-TCCC 512MB * 2 (DDR333-2.5-3-3-7) 外部記憶装置 HGST HDS722516VLAT80 * 2(160GB RAID1/Promise FastTrack TX2000) 電源装置 Seasonic SS-460HS/S オペレーティングシステム FreeBSD-4.11-STABLE 局所発振器 Kinseki(KSS) VC-TCXO-43C with Maxim MAX6325CSA voltage reference 特記事項 kernel compiler and its options

gcc version 2.95.4 20020320 [FreeBSD]

COPTFLAGS = -O -march=pentium

Hyper Threading Technology is enabled by sysctl and in the BIOS settings.

machdep.hlt_logical_cpus=0

machdep.hyperthreading_allowed=1

The parallel port is set to the ECP mode in the BIOS.

| [fig.28 VC-TCXO] | [fig.29 TCXO buffer] | [fig.30 Clock generator] |

|

|

|

| [fig.31 PPS→Echo delay (D.U.T.3, fcore=3.06GHz)] | [fig.32 PPS→Echo jitter (D.U.T.3, fcore=3.06GHz)] |

|

|

Agilent 53131A にて計測したところサンプル数 N=900, Vth=1.4V で、PPS→Echo の遅延は、PPS パルス幅を含み

であった。内部クロックが 3.06GHz に速くなったにもかかわらず応答時間は D.U.T.2(Pentium4-2.4C) よりも遅くなっていて、 またジッタも増大している。tdPPS↑Echo↓= 32.7688μs (σ=893.1ns) tpwEcho↓Echo↑=1.1386μs (σ=57.7ns)

この増大してたジッタだが、 前のマザーボードでは ICS のクロックジェネレータ

にヒートシンクを張り付けていたので、同様にヒートシンクを張り付けたところ

元のレベルに改善した。

温度によるクロックジェネレータの入力ピンのところの容量の変動が

バッファを介して僅かに VCTCXO に影響を与えていたと思われる。

[May. 12, 2012]

ntp サーバー運用終了。

NICT のハードウェア ntp サーバーが複数安定運用されるようになったのと、

サーバー老朽化及び ntp への DOS アタック増大により ntp はお役御免とした。

HP Z3816A は計測器の周波数基準用に現在も使用継続中。

[Apr. 11, 2022]

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.