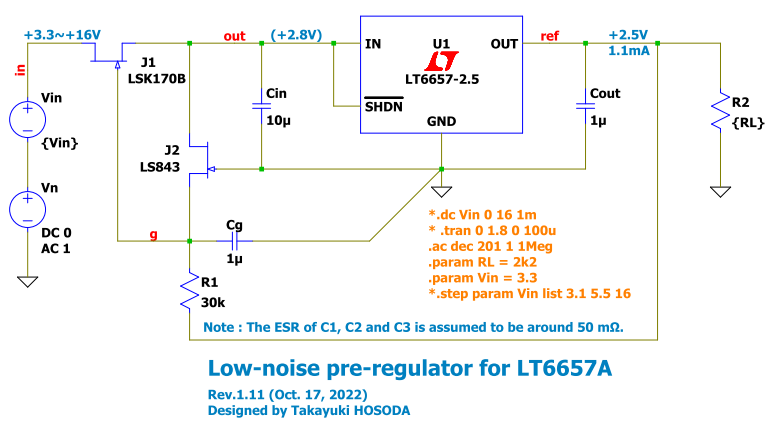

J1 is a high-gm ultra-low noise JFET and operates as a preregulator for U1, where the output voltage Vout is the reference voltage output Vref of U1 + the gate-to-source voltage Vgs of J1.

J2 operates as a start-up circuit.

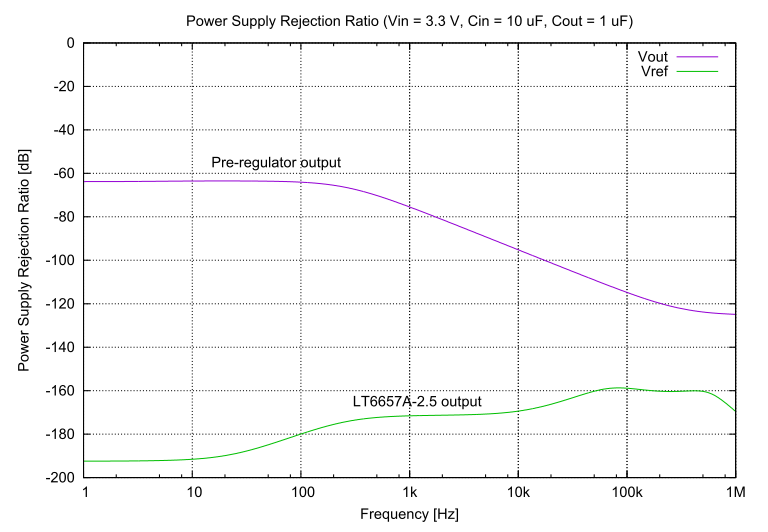

The output resistance of FET J1 ≈ 1 / gmOP at the operating point and Cin constitute the LPF.

Though the actual voltage tolerance of J1 is 40 V, the input voltage Vin is limited by the maximum load current, ambient temperature, and thermal dissipation conditions. In this example, the upper limit is taken to be 16 V.

Japanese edition is here.

Japanese edition is here.

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.