.func function_name(parameter1, parameter2, ...) { formula }

とします。定義した関数を素子のパラメータとして呼び出して使うには、素子値に { } をつけてその中身を LTspice に評価させます。

{ function_name(parameter1, parameter2, ...) }

また、LTspice では次の定数が利用できます。

- E : 2.7182818284590452354 — ネイピア数

- Pi : 3.14159265358979323846 — 円周率

- K : 1.3806503e-23 — ボルツマン定数

- Q : 1.602176462e-19 — 素電荷

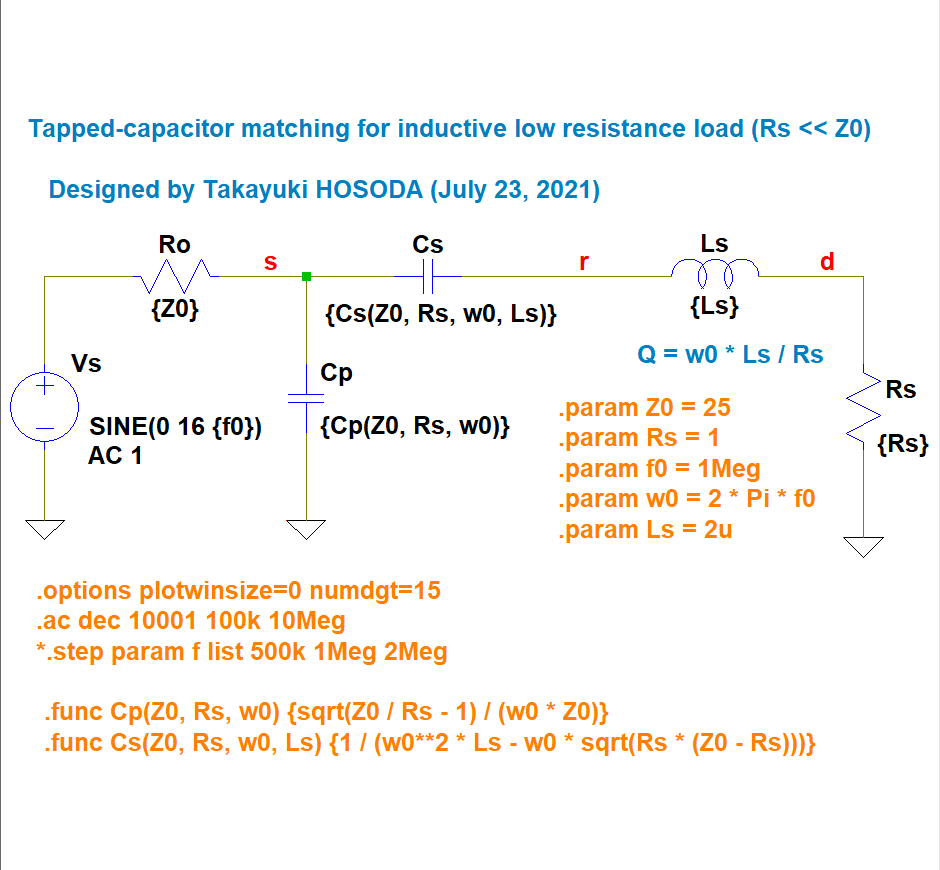

Download tapped-capacitor-matching.asc, the schematic file for the LTspice XVII.

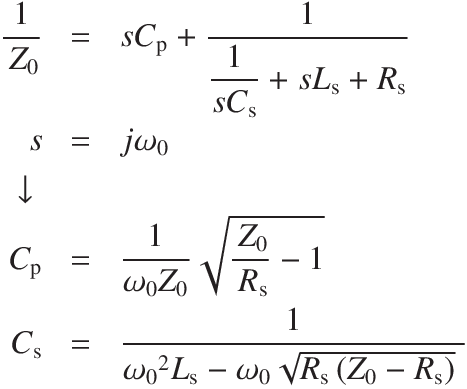

使用した数式

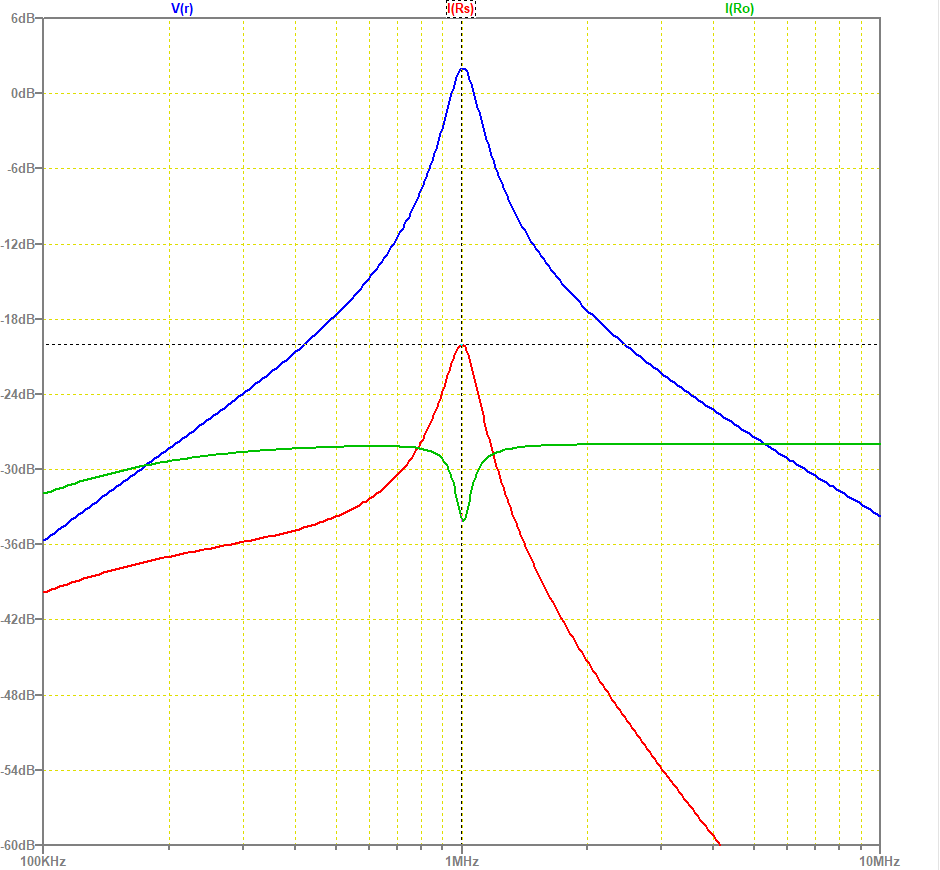

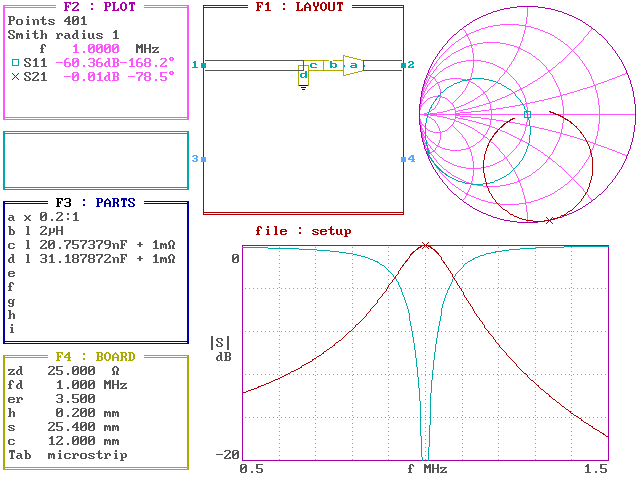

容量分割整合回路の周波数特性 (参考)

計算通り f0 = 1 MHz で Rs の電流値が最大になっているのが見て取れます。

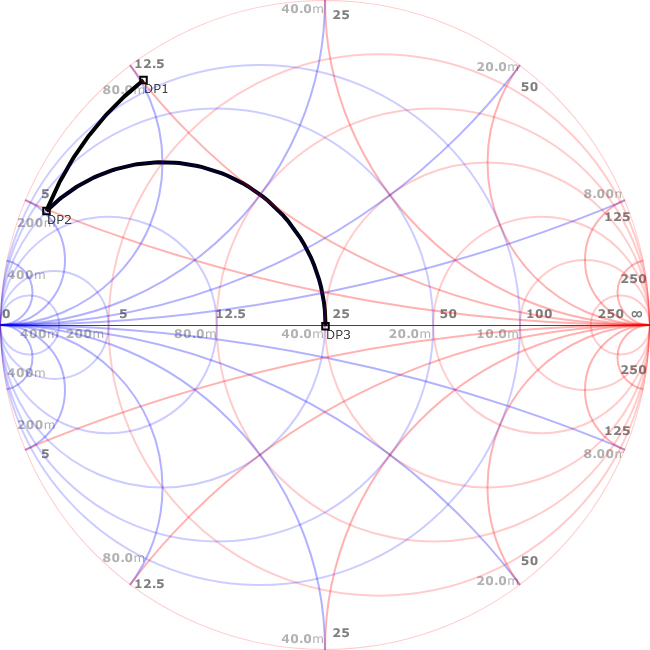

回路解説 — イミッタンスチャート上での軌跡 (参考)

回路例では Rs + Ls のインピーダンス (上図中 DP1) を Cs で 1/Z0 の定アドミタンス円上の点 (DP2) に移し、

Cp で誘導性のサセプタンス分を相殺して信号源インピーダンス Z0 の点 (DP3) に整合させています。

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.