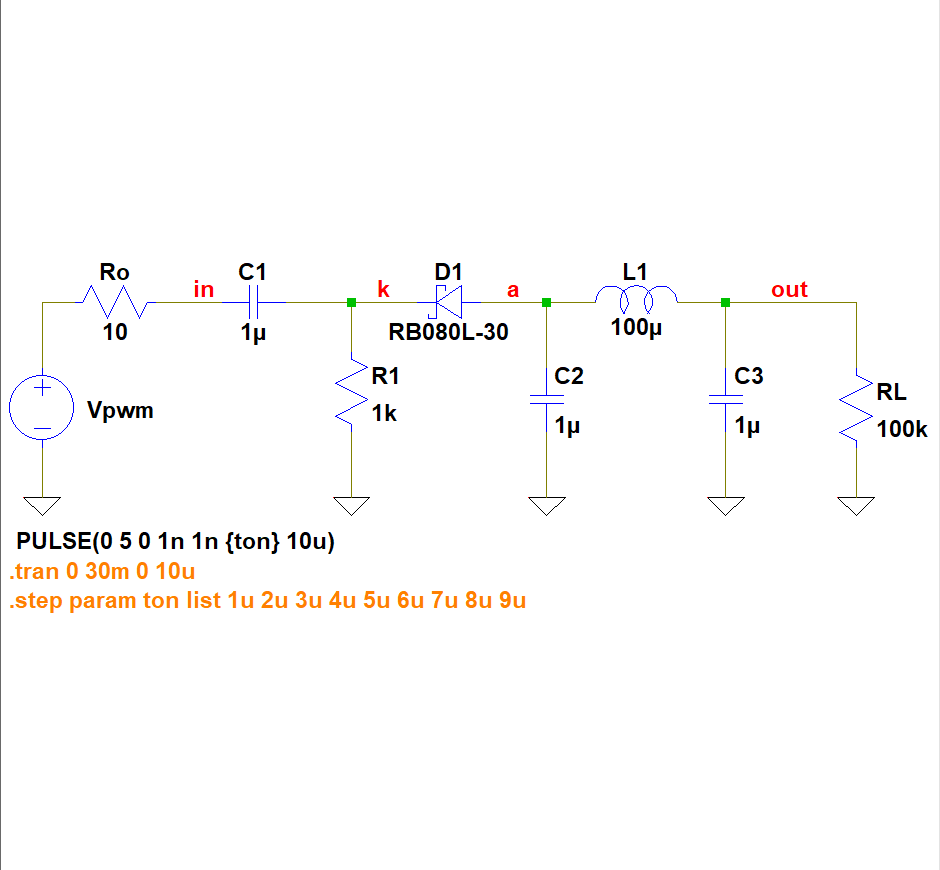

回路図中 C1, C2 は極性反転用キャパシタで、D1 は低Vf の整流用ショットキーバリアダイオードです。

Ro は保護抵抗兼 EMC 低減用抵抗です。 L1, C3 は出力の雑音を低減するためのローパスフィルタです。

PWM controlled negative voltage generator

Download lpf3mos-0.2.asc, the schematic file for the LTspice XVII.

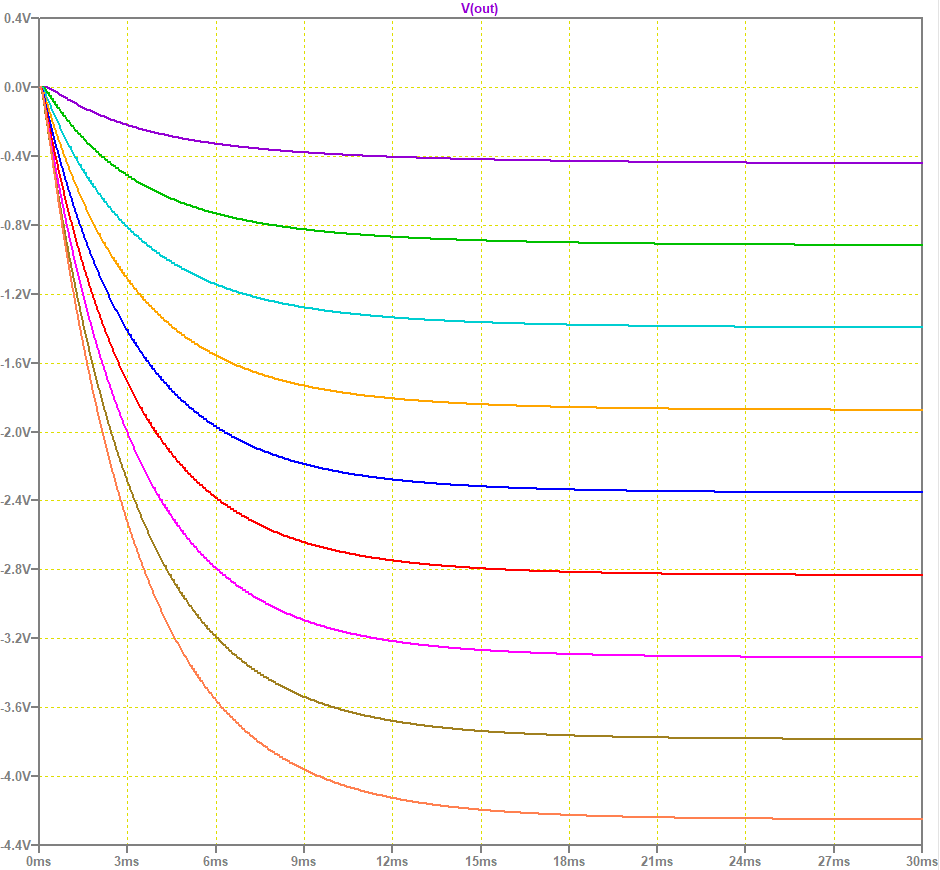

Step response

信号源は 5 V 電源の 74ACT125 のような CMOS バッファを想定しています。

回路図中 C1, C2 は極性反転用キャパシタで、D1 は低Vf の整流用ショットキーバリアダイオードです。

Ro は保護抵抗兼 EMC 低減用抵抗です。 L1, C3 は出力の雑音を低減するためのローパスフィルタです。

PWM controlled negative voltage generator

Download lpf3mos-0.2.asc, the schematic file for the LTspice XVII.

Step response

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.