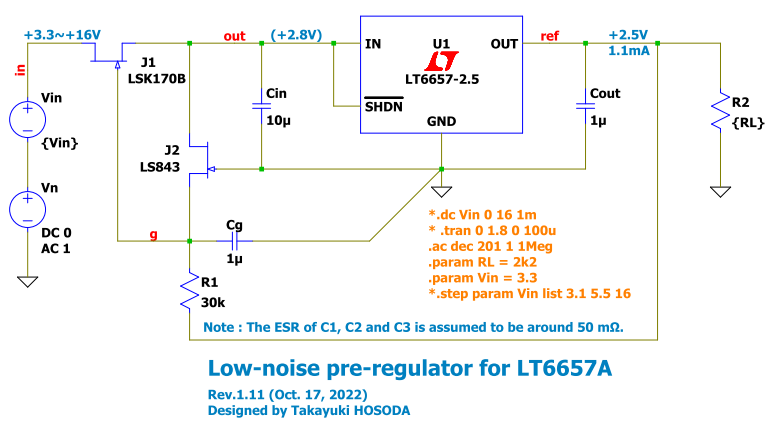

J1 は高 gm の超低雑音 JFET で、U1 に対し、出力電圧 Vout が U1 の基準電圧出力 Vref + J1 のゲート・ソース間電圧 Vgs になるプリレギュレータとして動作します。

J2 は起動回路として動作します。

また動作点における FET J1 の出力抵抗 ≒ 1/gmOP と Cin により LPF を構成しています。

J1 の実デバイスの耐圧は 40V ですが入力電圧 Vin は最大負荷電流と周囲温度や放熱条件等により制限されます。ここでは仮に 16 V を上限としています。

English edition is here.

English edition is here.

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.